### (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2015/0137132 A1

May 21, 2015 (43) **Pub. Date:**

### (54) ELECTROLUMINESCENCE DISPLAY DEVICE

(71) Applicant: Semiconductor Energy Laboratory Co., Ltd., Atsugi-shi (JP)

(72) Inventors: Koji ONO, Atsugi (JP); Hideomi SUZAWA, Atsugi (JP); Tatsuya ARAO, Atsugi (JP)

(21) Appl. No.: 14/589,369

(22) Filed: Jan. 5, 2015

### Related U.S. Application Data

(60) Continuation of application No. 14/223,366, filed on Mar. 24, 2014, now Pat. No. 8,957,424, which is a continuation of application No. 14/027,871, filed on Sep. 16, 2013, now Pat. No. 8,729,557, which is a continuation of application No. 13/185,989, filed on Jul. 19, 2011, now Pat. No. 8,569,767, which is a continuation of application No. 12/501,801, filed on Jul. 13, 2009, now Pat. No. 8,120,039, which is a continuation of application No. 11/305,212, filed on Dec. 19, 2005, now Pat. No. 7,560,734, which is a division of application No. 10/645,516, filed on Aug. 22, 2003, now Pat. No. 7,008,828, which is a division of application No. 09/714,891, filed on Nov. 17, 2000, now Pat. No. 6,646,287.

#### (30)Foreign Application Priority Data

Nov. 19, 1999 (JP) ...... 11-330174

### **Publication Classification**

(51) Int. Cl. H01L 27/12 (2006.01)

U.S. Cl. CPC ...... *H01L 27/1222* (2013.01)

#### ABSTRACT (57)

Disclosed is an electroluminescence device having a substrate, a thin film transistor over the substrate, an insulating film over the thin film transistor, an electroluminescence element over the insulating film, a passivation film over the electroluminescence element, and a counter substrate over the passivation film. The electroluminescence element is configured to emit light through the counter substrate, and a space between the substrate and the counter substrate is filled with a filler. The electroluminescence device is featured by the tapered side surface of a gate electrode of the thin film tran-

Fig.7A

Fig.7B

Fig.8A

Fig.8B

Fig.15

Fig.16

Fig.18

Fig.21A

Fig.21B

Fig.24B

Fig.24C

FIG. 27

FIG. 28

FIG. 29

FIG. 30

# ELECTROLUMINESCENCE DISPLAY DEVICE

### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] The present invention relates to a semiconductor device having a circuit structured by a thin film transistor (hereafter ref ed to as a TFT) on a substrate having an insulating surface, and to a method of manufacture thereof. In particular, the present invention provides an electro-optical device, typically a liquid crystal display device or an EL display device in which a pixel portion and a driver circuit are formed on the same substrate, and provides a technique of suitably utilizing this type of electro-optical device loaded into electronic equipment. Note that, throughout this specification, the term semiconductor device indicates a general device functioning by utilizing semiconductor characteristics, and the above electro-optical device, and equipment in which the electro-optical device is loaded, are included in the category of semiconductor device.

[0003] 2. Description of the Related Art

[0004] A display device structured by a pixel portion in which active elements are arranged is referred to as an active matrix display device, and devices such as a liquid crystal display device and an electroluminescence (hereafter referred to as EL) display device have been developed. An insulating gate type transistor is used in an active element, and a TFT is used ideally. A semiconductor film is formed on a substrate such as glass by a method such as a vapor phase growth method, and, using the semiconductor film, regions such as a channel forming region, a source region, and a drain regions are formed for the TFT. Ideally a material having silicon as its main constituent, such as silicon or silicon germanium is used in the semiconductor film. Semiconductor films can be classified into amorphous semiconductor films, typically amorphous silicon, and into crystalline semiconductor films, typically polycrystalline silicon, in accordance with their method of manufacture. In addition, techniques for structuring a pixel portion by insulating gate type transistors formed on a single crystal silicon substrate have been developed in recent years. [0005] It is nearly impossible to obtain an electric field effect mobility equal to or greater than  $10 \text{ cm}^2/\text{V} \cdot \text{sec}$  in a TFT in which an active layer is formed by an amorphous semiconductor (typically amorphous silicon) film due to electrical solid state factors such as the amorphous crystal structure. Therefore, even though they can be used as switching elements for driving a liquid crystal in the pixel portion in an active matrix type liquid crystal display device (switching elements formed by TFTs are hereafter referred to as pixel TFTs), it is impossible to use them to form a driver circuit for performing image display. Consequently, a driver IC is implemented by using a technique such as TAB (tape automated bonding) or COG (chip on glass).

[0006] On the other hand, with a TFT having a semiconductor film, typically a crystalline silicon or a polycrystalline silicon, containing a crystalline structure (hereafter referred to as a crystalline semiconductor) as an active layer, a high electric field effect mobility can be obtained, and therefore this type of TFT can form all types of functional circuit and can perform driving. It therefore becomes possible to realize a pixel TFT and, on the same substrate, circuits such as a shift register circuit, a level shifter circuit, a buffer circuit, and a sampling circuit in a driver circuit. The driver circuit is formed by CMOS circuits, composed of n-channel TFTs and

p-channel TFTs, as basic units. Techniques of implementing this type of driver circuit are fundamental, and in order to promote making lower weight and thinner liquid crystal display devices, it is thought that a TFT having a crystalline semiconductor layer as an active layer, in which it is possible to form the driver circuit, in addition to the pixel portion, on the same substrate, is suitable.

[0007] Forming the active layer by a crystalline semiconductor layer is superior when comparing TFT characteristics, but there are problems in that the manufacturing process becomes complex, and the number of process steps increases, in order to manufacture a TFT corresponding to each circuit in addition to the pixel TFT. It is clear that the increase in the number of process steps is a cause of increased manufacturing costs, and that it leads to a drop in the manufactured yield.

[0008] The operating conditions of the pixel TFTs and driver circuit TFTs are not necessarily the same, and therefore the required characteristics of the TFTs also differ greatly. A pixel TFT formed by an n-channel TFT is a switching element which drives a liquid crystal by applying a voltage. The liquid crystal is driven by an AC current therefore a method referred to as frame inversion drive is employed. The pixel TFT is required to have a sufficiently low Off current (the drain current flowing when the TFT is in off operation) in order to maintain an electric charge which has accumulated in a liquid crystal layer for the duration of one frame period. On the other hand, a high driver voltage is applied to the driver circuits, such as a buffer circuit, and therefore a high voltage resistance is required so that the circuit is not damaged due to the high voltage application. Further, in order to increase the electric current driver performance, it is necessary to secure a sufficient value of the On current (the drain current flowing when the TFT is in on operation).

[0009] An LDD (lightly doped drain) structure is known as a TFT structure for reducing the value of the Off current. This structure is one in which a region having a low concentration of an added impurity element is formed between a channel forming region and a source region or drain region having a high concentration of an added impurity element, and the low concentration region is referred to as an LDD region. Further, there is a GOLD (gate-drain overlapped LDD) structure, in which the LDD region is arranged so as to overlap a gate electrode through a gate insulating film, as a means of preventing degradation of the On current value due to a hot carrier. It is known that using this type of structure is effective in preventing deterioration phenomena by relieving the high electric field near a drain and protecting against hot carrier injection.

[0010] However, the bias state of the pixel TFT and driver circuit TFTs such as those of a shift register circuit and a buffer circuit are not necessarily the same. For example, a large inverse bias is applied to the gate in the pixel TFT (a negative voltage for an n-channel TFT), but driver circuit TFTs basically will not operate in an inverse bias state. Further, the GOLD structure is effective in protecting against degradation of the On current value, but the value of the Off current becomes large by simply overlapping with the gate electrode. On the other hand, although the Off current value control effect is high for a normal LDD structure, it has low effectiveness in relieving the electric field in the vicinity of the drain and therefore in preventing deterioration due to hot carrier injection. This type of problem becomes more tangible, the more the characteristics increase, and the higher the required functionality of the active matrix type liquid crystal

display device, particularly in a crystalline silicon TFT. Therefore, considering the different TFT operating state, and considering the prevention of the above hot carrier effect, it is necessary to optimize parameters such as the impurity element concentration of the LDD region, and its distribution.

### SUMMARY OF THE INVENTION

[0011] The present invention is a technique of solving the above problems, and an object of the present invention is to realize an improvement in the operating characteristics and the reliability of a semiconductor device by using appropriate structures, in accordance with circuit function, for TFTs arranged in each circuit of the semiconductor device, typically an active matrix type display device manufactured by using TFTs. In addition, an object of the present invention is to realize a reduction in manufacturing costs, and an increase in yield, by reducing the number of process steps.

[0012] In order to realize a reduction in manufacturing costs and an increase in yield, reducing the number of process steps is one means which can be applied. Specifically, it is necessary to reduce the number of photomasks required for TFT manufacture. Photomasks are used in order to form a resist pattern which serves as an etching mask in a photolithography technique, on a substrate. To use one of these photomasks, in addition to steps such as film formation and etching, there are additional steps such as those of resist peeling, cleaning, and drying, and even in the photolithography process, complex steps such as resist application, prebaking, exposure, development, and post baking are performed.

[0013] Even while reducing the number of photomasks, the structure of TFTs arranged in each type of circuit is made appropriate in correspondence with the function of the circuit. Specifically, a structure which places emphasis on reducing the value of the Off current more than on operation speed is preferable for a pixel TFT. A multi-gate structure is employed as that type of structure. On the other hand, for a TFT forming a driver circuit in which high speed operation is demanded, it is necessary to use a structure which increases the operation speed and which, at the same time, places emphasis on controlling the conspicuous problem of degradation due to hot carrier injection. This structure is realized by an LDD region of a novel configuration. To be specific, a concentration gradient of an impurity element for controlling conductivity is set in the LDD region formed between a channel forming region and the drain region such that the concentration increases as the distance from the drain region decreases. Thus, an effect can be increased in which the concentration of an electric field in a depletion layer near the drain region is relieved. A portion of the LDD region may also be formed so as to overlap a gate electrode.

[0014] In order to form an LDD region having an above-described concentration gradient of an impurity element, a method of doping into a semiconductor layer is used, in which an ionized impurity element for controlling conductivity is accelerated by an electric field, and made to pass through a portion of the gate electrode and a gate insulating film (a gate insulating film formed between the gate electrode and the semiconductor layer, and in close contact with both, and an insulating film extending in a region in the periphery of the gate insulating film, is included in the term gate insulating film for the present invention). In addition, the gate electrode is tapered so that the thickness thereof gradually increases from an edge portion of the gate electrode toward the inside,

and concentration of the impurity element doped into the semiconductor layer is controlled by utilizing that change in thickness. Namely, the LDD region is formed so that the concentration of the impurity element gradually changes toward the longitudinal direction of the TFT channel.

[0015] Specifically, a first etching process is performed for a conductive layer forming the gate electrode, a predetermined region of the conductive layer is removed, and the gate insulating film is exposed in a portion of the region on the semiconductor layer. The conductive layer has a tapered shape at this point in which its thickness gradually increases firm the edge portion toward the inside. A first doping process for adding a single conductivity type impurity element is then performed, and the formation of a first low concentration impurity region is performed. Next, a second etching process and a second doping process are similarly performed, and the formation of a second low concentration impurity region is performed. The LDD region is formed from the first and the second low concentration impurity regions. In this case the shape of the gate electrode is determined in accordance with the second etching process, and provided that suitable conditions for the second doping process are selected, a portion of the LDD region can be formed so as to overlap with the gate electrode.

[0016]  $\,$  The LDD region is thus formed in the present invention by repeating etching and doping processes a plurality of times. As a result, a plurality of LDD regions in which the concentration with respect to the longitudinal direction of the channel differs, and the impurity element concentration of the LDD region can be changed stepwise or continuously.

[0017] It is preferable to use a heat resistant conductive material for the conductive layer forming the gate electrode, and the conductive layer is formed from an element selected from the group consisting of tungsten (W), tantalum (Ta), and titanium (Ti), or from a compound or an alloy having the above elements as constituents. In order to etch this heat resistant conductive material at high speed and with good precision, and in addition, in order to form a tapered shape in the edge portion, it is preferable to apply a dry etching method using a high density plasma. An etching apparatus using microwaves or an inductively coupled plasma (ICP) is suitable as a means for obtaining the high density plasma. In particular, it is easy to control the plasma in an ICP etching apparatus, and it can also respond to a large surface area substrate.

[0018] As described above, according to a structure of the present invention, a semiconductor device having a semiconductor layer, an insulating film formed contacting the semiconductor layer, and a gate electrode having a tapered portion on the insulating film, is characterized in that:

[0019] the semiconductor layer has: a channel forming region; a first impurity region forming a source region or a drain region containing a single conductivity type impurity element; and a second impurity region forming an LDD region contacting the channel forming region;

[0020] a portion of the second impurity region is formed overlapping a gate electrode; and

[0021] the concentration of the single conductivity type impurity element contained in the second impurity region increases as distance from the channel forming region increases.

[0022] This structure of the present invention can be suitably used in a semiconductor device in which TFTs are formed on a substrate. According to another structure of the

present invention, a semiconductor device having an n-channel TFT and a p-channel TFT, is characterized in that:

- [0023] the semiconductor layer of the n-channel TFT has: a channel forming region; a first impurity region forming a source region or a drain region containing a single conductivity type impurity element; and a second impurity region forming an LDD region contacting the channel forming region;

- [0024] a portion of the second impurity region is formed overlapping a gate electrode;

- [0025] the concentration of the single conductivity type impurity element contained in the second impurity region increases as distance from the channel forming region increases;

- [0026] the semiconductor layer of the p-channel TFT has: a channel forming region; a third impurity region forming a source region or a drain region; and a fourth impurity region forming an LDD region contacting the channel forming region; and

- [0027] the single conductivity type impurity element and an impurity element, having a conductivity type which is inverse to the conductivity type of the single conductivity type impurity element, are contained in the third impurity region and the fourth impurity region.

[0028] A semiconductor device having a pixel portion is characterized in that:

[0029] the semiconductor layer of at least one TFT formed in each pixel of the pixel portion has: a channel forming region; a first impurity region forming a source region or a drain region containing a single conductivity type impurity element; and a second impurity region forming an LDD region contacting the channel forming region;

- [0030] a portion of the second impurity region is formed overlapping a gate electrode; and

- [0031] the concentration of the single conductivity type impurity element contained in the second impurity region increases as distance from the channel forming region increases.

- [0032] According to the present invention, a method of manufacturing a semiconductor device of the present invention has:

- [0033] a first step of forming an insulating film on a semiconductor layer;

- [0034] a second step of forming a conductive layer on the insulating film;

- [0035] a third step of selectively etching the conductive layer, forming a conductive layer having a first tapered shape.

- [0036] a fourth step of doping a single conductivity type impurity element into the semiconductor layer, after completing the third step;

- [0037] a fifth step of selectively etching the conductive layer having the first tapered shape, forming a conductive layer having a second tapered shape; and

- [0038] a sixth step of doping a single conductivity type impurity element into the semiconductor layer, after completing the fifth step,

[0039] the method being characterized in that the concentration of the single conductivity type impurity element doped in the sixth step is lower than the concentration of the single conductivity type impurity element doped in the fourth step. [0040] This structure of the present invention can be suitably used in a semiconductor device in which TFTs are formed on a substrate. According to another structure of the

present invention, a method of manufacturing a semiconductor device having an n-channel thin film transistor and a p-channel thin film transistor, has:

- [0041] a first step of forming an insulating film on a semiconductor layer of the n-channel thin film transistor and that of the p-channel thin film transistor,

- [0042] a second step of forming a conductive layer on the insulating film;

- [0043] a third step of selectively etching the conductive layer, to form a conductive layer having a first tapered shape:

- [0044] a fourth step of doping a single conductivity type impurity element into the semiconductor layers, after completing the third step;

- [0045] a fifth step of selectively etching the conductive layer having the first tapered shape, to form a conductive layer having a second tapered shape;

- [0046] a sixth step of doping a single conductivity type impurity element into the semiconductor layers, after completing the fifth step; and

- [0047] a seventh step of doping an impurity element, having a conductivity type which is inverse to the conductivity type of the single conductivity type impurity element, into the semiconductor layer of the p-channel thin film transistor, after completing the sixth step,

[0048] the method being characterized in that the concentration of the single conductivity type impurity element doped in the sixth step is lower than the concentration of the single conductivity type impurity element doped in the fourth step. [0049] According to still another structure of the present invention, a method of manufacturing a semiconductor device having a pixel portion has:

- [0050] a first step of forming an insulating film on semiconductor layer that forms a TFT provided in each pixel portions;

- [0051] a second step of forming a conductive layer on the insulating film;

- [0052] a third step of selectively etching the conductive layer, forming a conductive layer having a first tapered shape;

- [0053] a fourth step of doping a single conductivity type impurity element into the semiconductor layer, after completing the third step;

- [0054] a fifth step of selectively etching the conductive layer having the first tapered shape, forming a conductive layer having a second tapered shape; and

- [0055] a sixth step of doping a single conductivity type impurity element into the semiconductor layer, after completing the fifth step,

[0056] the method being characterized in that the concentration of the single conductivity type impurity element doped in the sixth step is lower than the concentration of the single conductivity type impurity element doped in the fourth step.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0057] In the accompanying drawings:

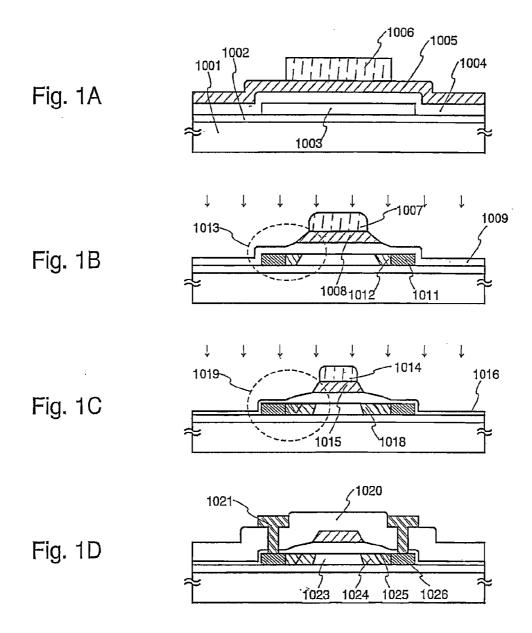

[0058] FIGS. 1A to 1D are diagrams for explaining a method of manufacturing a TFT of the present invention;

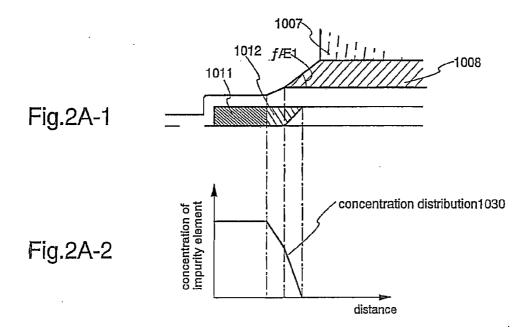

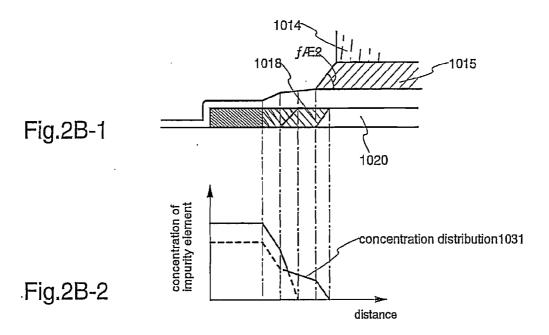

[0059] FIGS. 2A-1 to 2B-2 are diagrams for explaining the concentration distribution of an impurity element in an LDD region corresponding to FIGS. 1A to 1D;

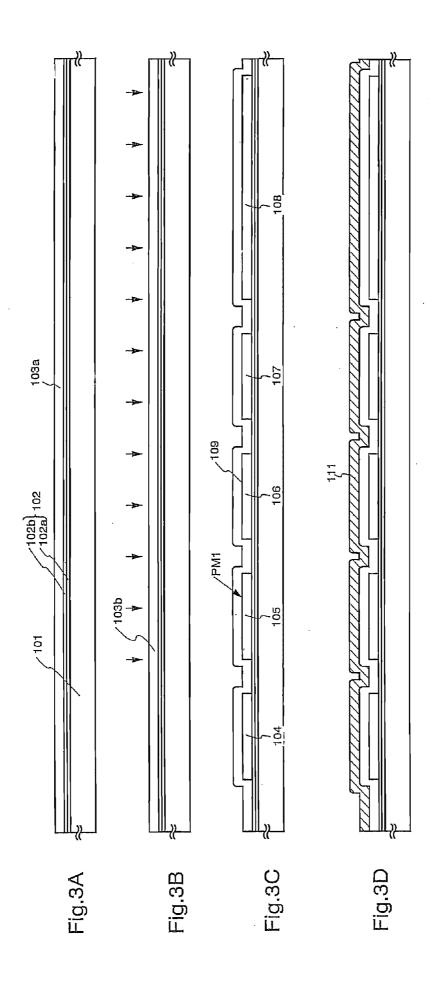

[0060] FIGS. 3A to 3D are cross sectional diagrams showing a method of manufacturing a pixel TFT and a driver circuit TFT:

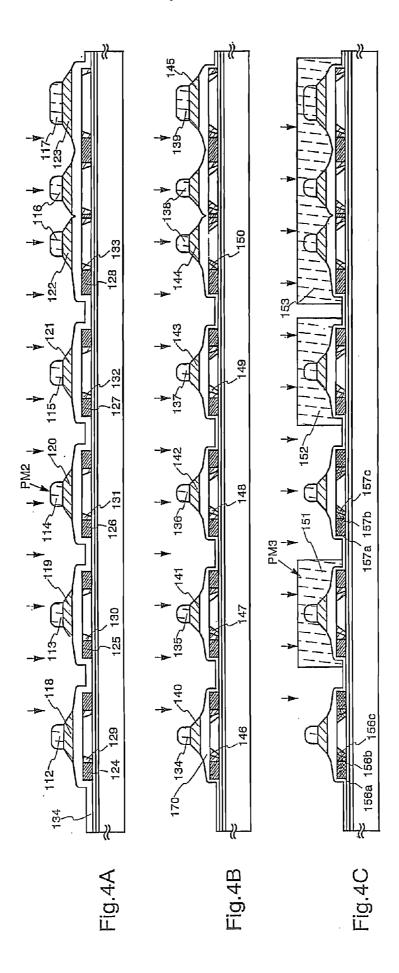

[0061] FIGS. 4A to 4C are cross sectional diagrams showing the method of manufacturing the pixel TFT and the driver circuit TFT;

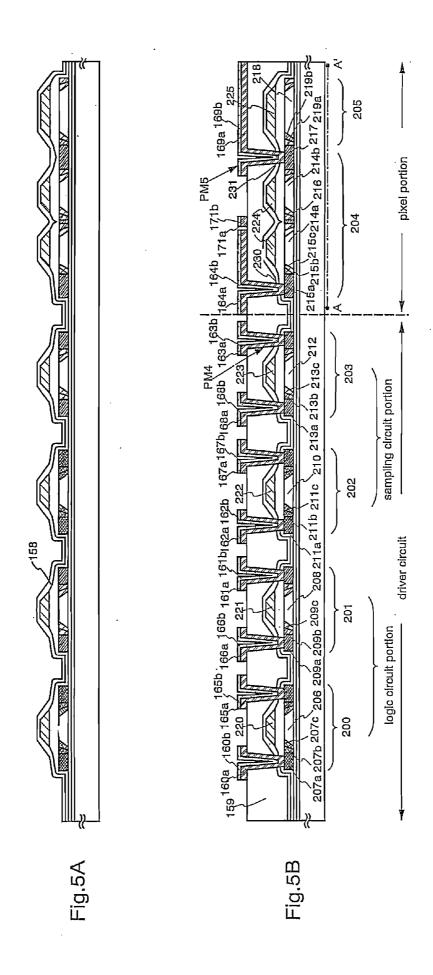

[0062] FIGS. 5A and 5B are cross sectional diagrams showing the method of manufacturing the pixel TFT and the driver circuit TFT;

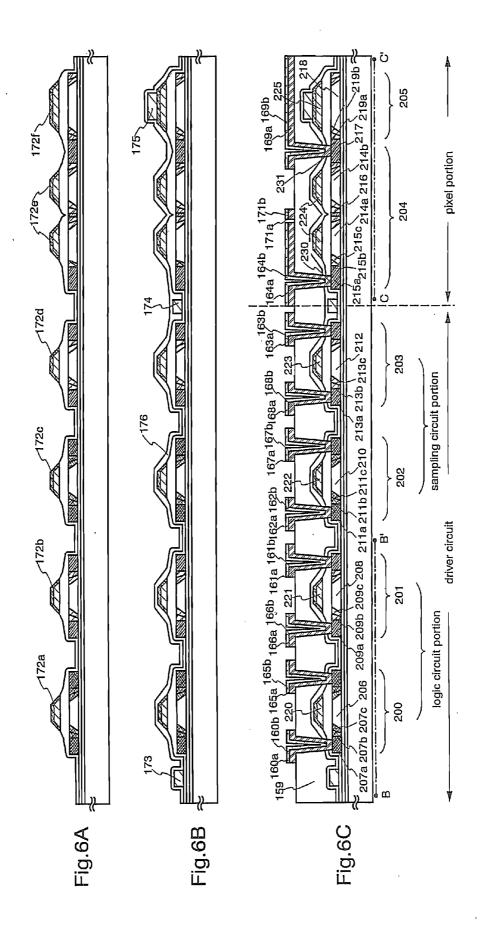

[0063] FIGS. 6A to 6C are cross sectional diagrams showing the method of manufacturing the pixel TFT and the driver circuit TFT;

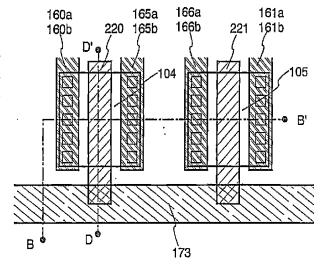

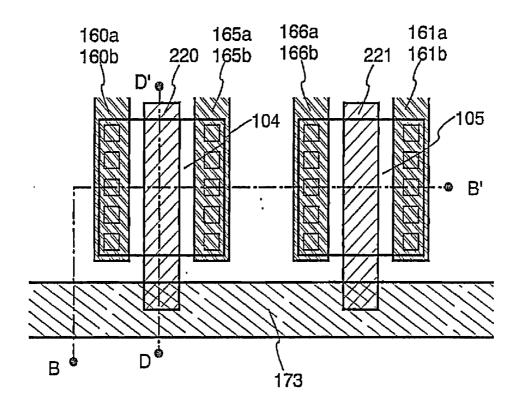

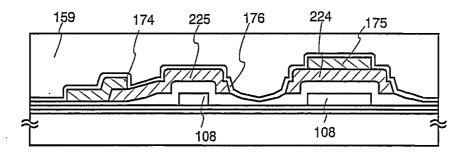

[0064] FIGS. 7A and 7B are top views showing the structure of a driver circuit TFT and the structure of a pixel TFF; [0065] FIGS. 8A and 8B are cross sectional diagrams showing the structure of a driver circuit TFT and the structure of a pixel TFT;

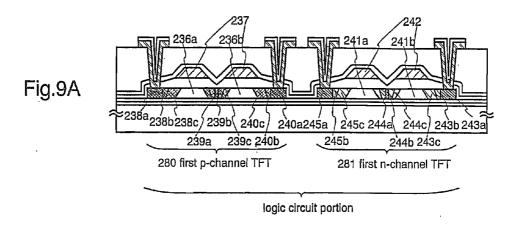

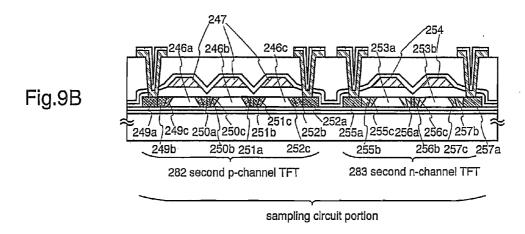

[0066] FIGS. 9A and 9B are cross sectional diagrams showing the structure of driver circuit TFTs;

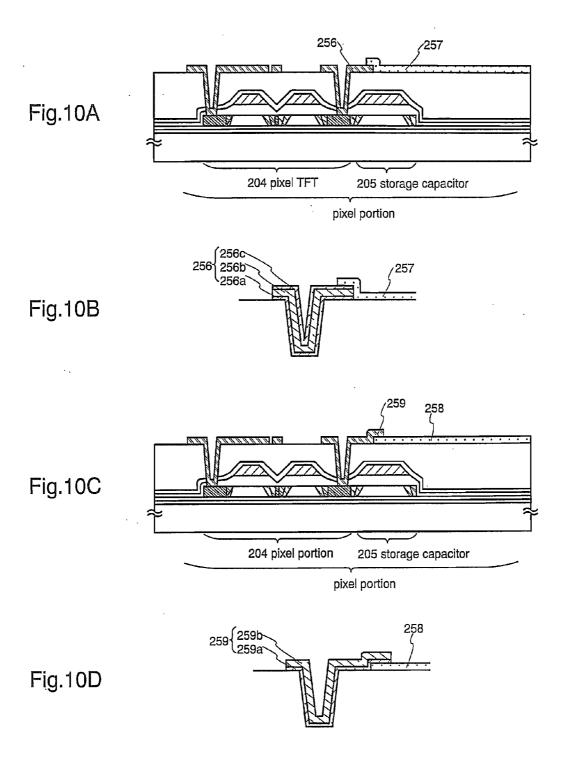

[0067] FIGS. 10A to 10D are cross sectional diagrams showing the structure of a pixel TFT;

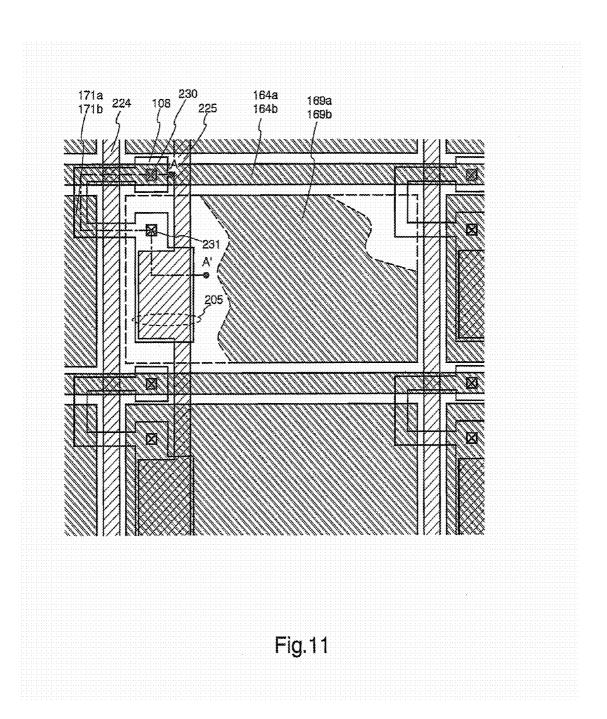

[0068] FIG. 11 is a top view showing a pixel of a pixel portion;

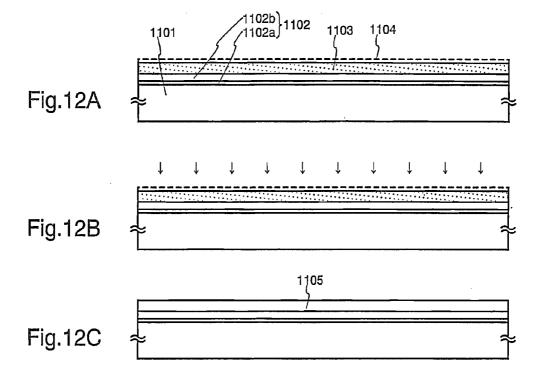

[0069] FIGS. 12A to 12C are cross sectional diagrams showing a process of manufacturing a crystalline semiconductor layer;

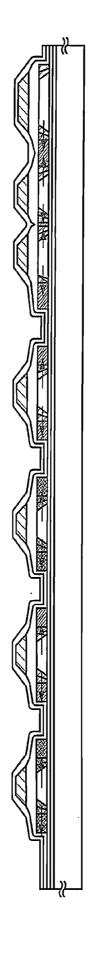

[0070] FIG. 13 is a cross sectional diagram showing a process of manufacturing a pixel TFT and a driver circuit TFT;

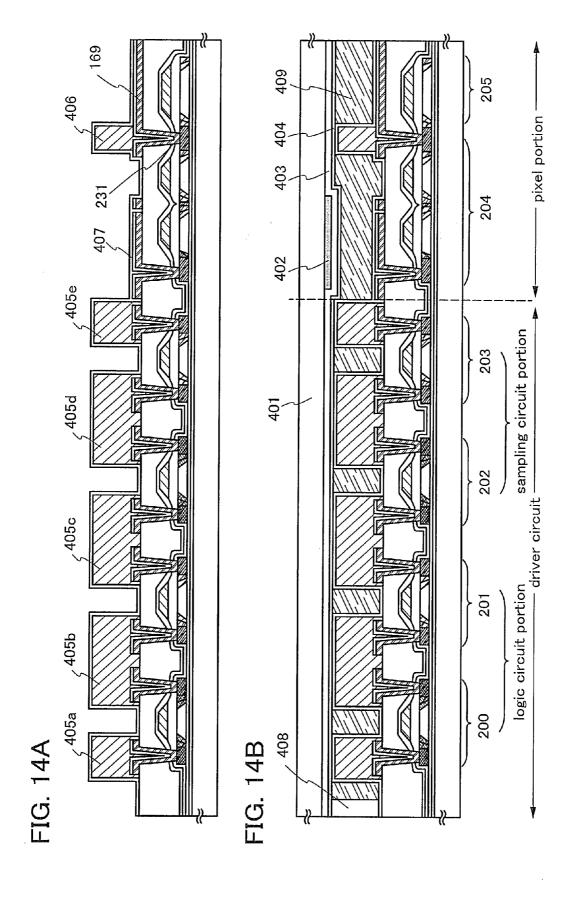

[0071] FIG. 14 are cross sectional diagrams showing a process of manufacturing an active matrix type liquid crystal display device;

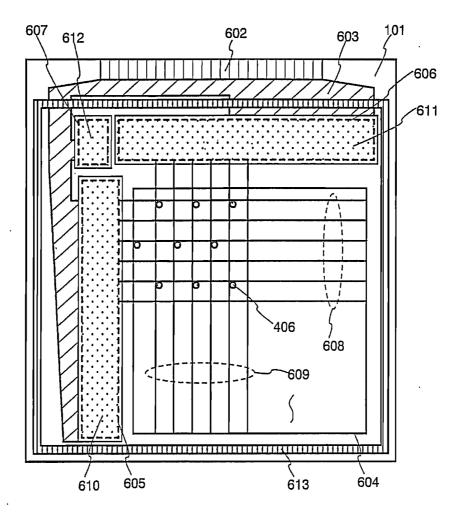

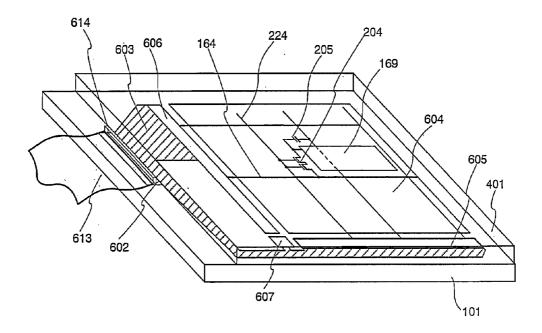

[0072] FIG. 15 is a top view for explaining an input-output terminal, a wiring, a circuit arrangement, a spacer, and a sealing material arrangement of a liquid crystal display device;

[0073] FIG. 16 is a perspective view showing a structure of a liquid crystal display device;

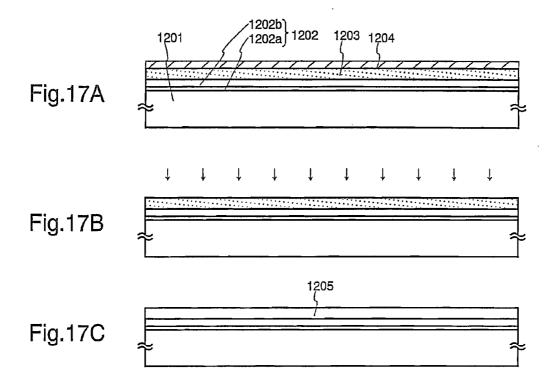

[0074] FIGS. 17A to 17C are cross sectional diagrams showing a process of manufacturing a crystalline semiconductor layer,

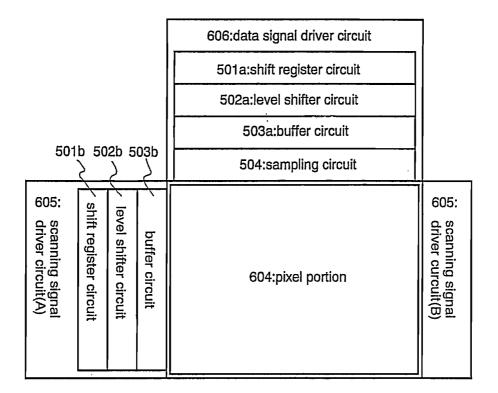

[0075] FIG. 18 is a block diagram for explaining a circuit structure of an active matrix type display device;

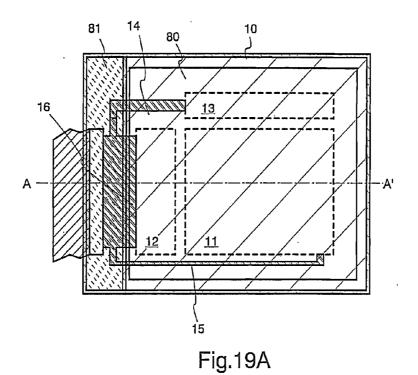

[0076] FIGS. 19A and 19B are a top view and a cross sectional diagram, respectively, showing a structure of an EL display device;

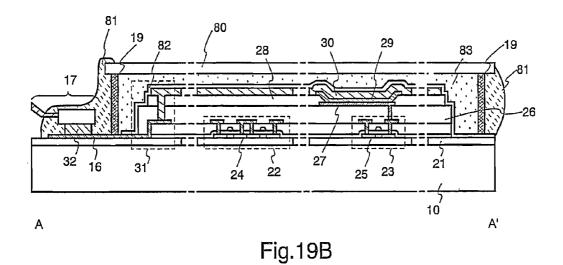

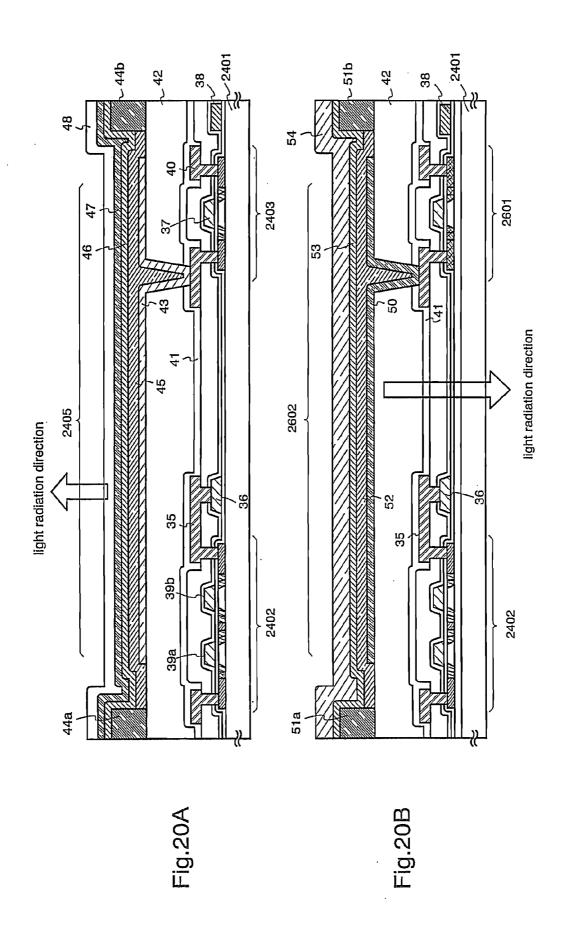

[0077] FIGS. 20A and 20B are cross sectional diagrams of a pixel portion of an EL display device;

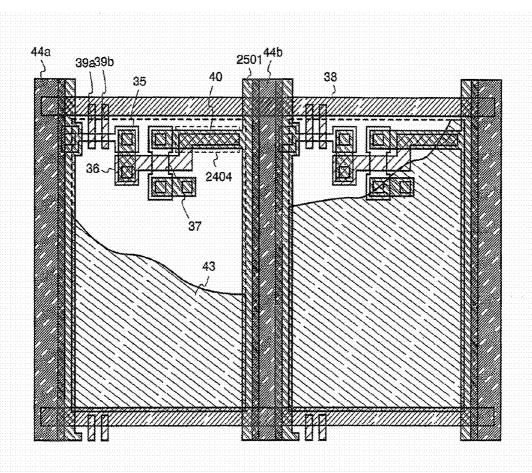

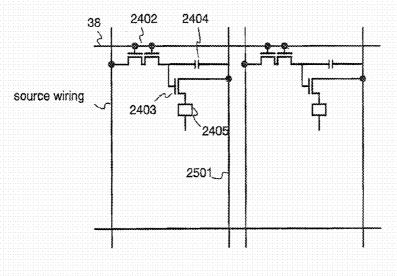

[0078] FIGS. 21A and 21B are a top view and a circuit diagram, respectively, of a pixel portion of an EL display device:

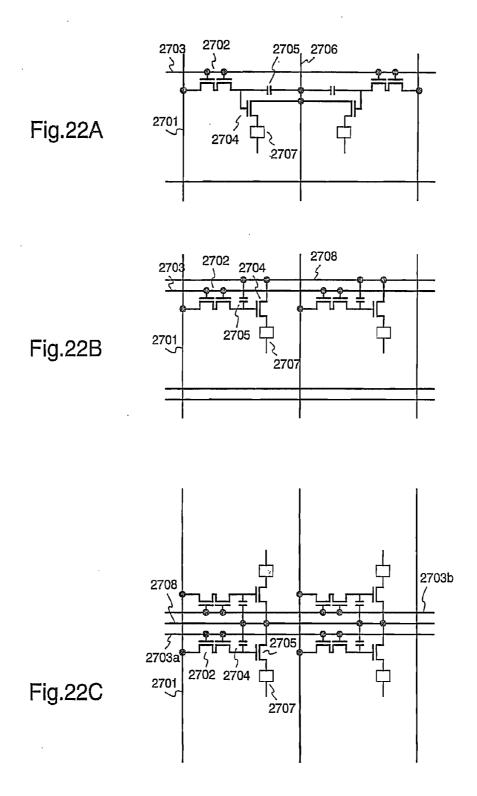

[0079] FIGS. 22A to 22C are examples of circuit diagrams of a pixel portion of an EL display device;

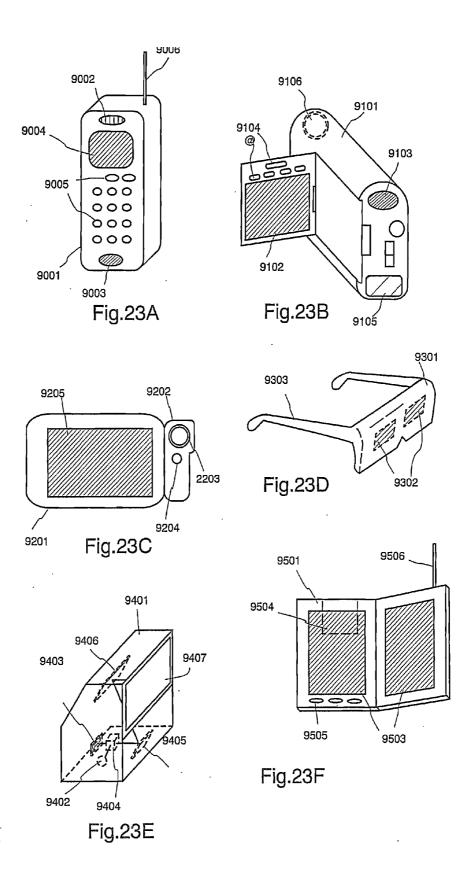

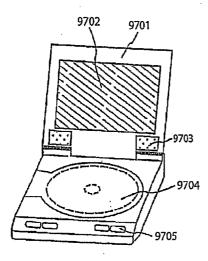

[0080] FIGS. 23A to 23F are diagrams showing examples of semiconductor devices;

[0081] FIGS. 24A to 24C are diagrams showing examples of semiconductor devices; and

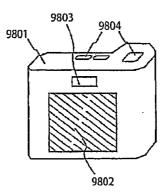

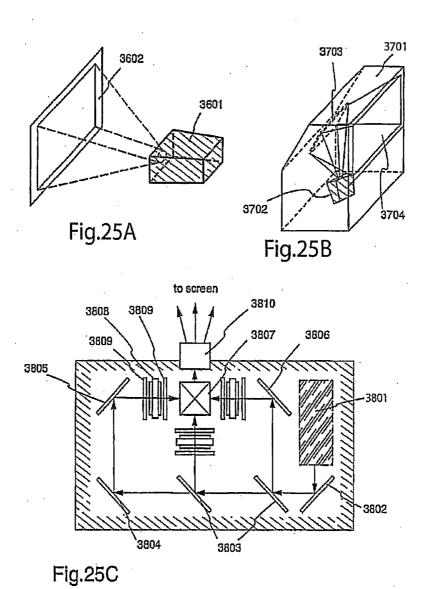

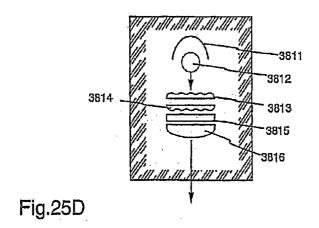

[0082] FIGS. 25A to 25D are diagrams showing a structure of a projecting type liquid crystal display device.

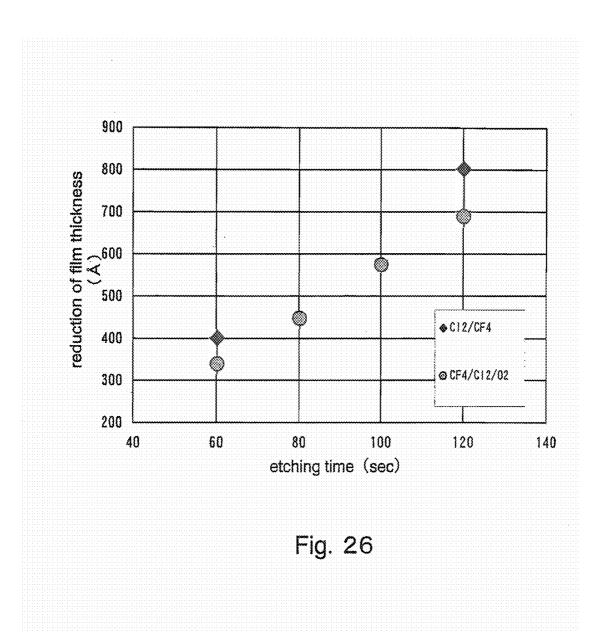

[0083] FIG. 26 is a graph showing a relation between the etching time and the decrease in the film thickness of silicon nitride oxide film.

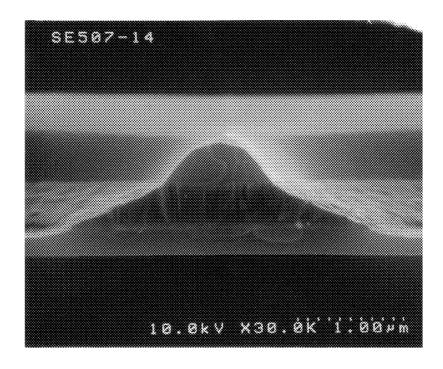

[0084] FIG. 27 is a cross sectional view of a tungsten film processed a first etching treatment which is obtained by SEM.

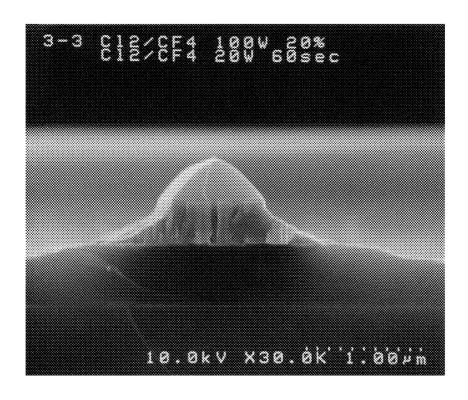

[0085] FIG. 28 is a cross sectional view of a tungsten film processed a second etching treatment using a mixture gas of CF<sub>4</sub> and Cl<sub>2</sub> which is obtained by SEM.

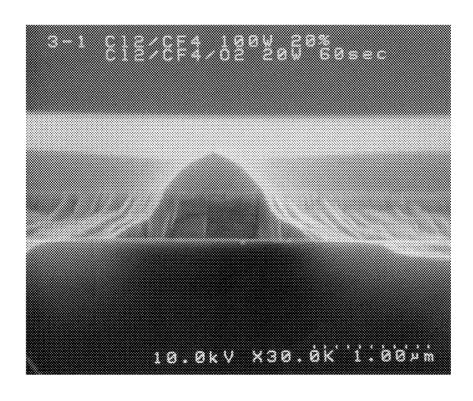

[0086] FIG. 29 is a cross sectional view of a tungsten film processed a second etching treatment using a mixture gas of CF4, Cl2 and O2.

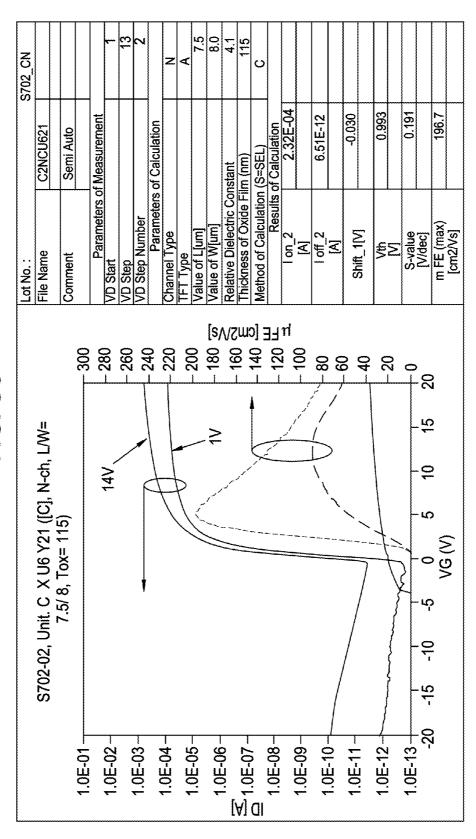

[0087] FIG. 30 is a graph showing a static property of the TET

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

### **Embodiment Mode**

[0088] An Embodiment mode of the present invention is explained using FIGS. 1A to 2B-2. In addition to a glass substrate such as barium borosilicate glass or aluminum borosilicate glass, typically Corning Corp. #7059 or #1737 glass, a plastic substrate not having optical anisotropy such as polyethylene terephthalate (PET), polyethylene naphthalate (PEN), or polyether sulfone (PES) can be used in a substrate 1001 in FIG. 1A. Further, a quartz substrate may also be used. If a heat treatment is performed in advance at a temperature on the order of 10 to 20° C. less than the distortion point of the glass, when using a glass substrate, then changes in shape of the glass substrate by subsequent processes can be prevented. [0089] A base film 1002, with a thickness of 10 to 200 nm, is formed from an insulating film such as a silicon oxide film, a silicon nitride film, or a silicon nitride oxide film on the surface of the substrate 1001 on which a TFT will be formed in order to prevent impurity element diffusion.

[0090] The base film may be formed by one layer of the insulating film, and may also be formed by a plurality of layers.

[0091] An island-like semiconductor layer 1003 is formed from a crystalline semiconductor film in which a semiconductor film having an amorphous structure is crystallized by a method such as laser annealing, thermal annealing, or rapid thermal annealing (RTA). Further, a crystalline semiconductor film formed by a method such as sputtering, plasma CVD, or thermal CVD may also be used. Alternatively, a crystalline semiconductor layer 103b can also be formed by a crystallization method using a catalytic element, in accordance with a technique disclosed by Japanese Patent Application Laidopen No. Hei 7-130652. In this crystallization process, first it is preferable to remove hydrogen contained in the amorphous semiconductor layer, and if crystallization is performed after the amount of hydrogen contained is made equal to or less than 5 atom % by performing a heat treatment at 400 to 500° C. for approximately 1 hour, then roughness of the film surface can be prevented. Whichever method is used, the crystalline semiconductor film thus formed is selectively etched, forming the island-like semiconductor layer 1003 in a predetermined place.

[0092] Alternatively, an SOI (silicon on insulator) substrate in which a single crystal silicon layer is formed on the substrate 1001 may also be used. There are known many types of SOI substrate which vary in structure and in manufacturing method, and typically an SOI substrate such as SIMOX (separation by implanted oxygen), ELTRAN (epitaxial layer transfer, a trademark of Canon Corp.) substrate, or Smart-Cut (a trademark of SOITEC Corp.) can be used. Of course, it is also possible to use other SOI substrates.

[0093] A gate insulating film is formed by a method such as plasma CVD, sputtering, or reduced pressure CVD from an insulating film containing silicon and having a thickness of 40 to 150 nm. For example, it may be formed from a film such as a silicon oxide film, a silicon nitride film, or a silicon nitride

oxide film. This is taken as a first shape gate insulating film 1004. A conductive layer 1005 is then formed on the first shape gate insulating film 1004 in order to form a gate electrode. It is preferable to form the conductive layer 1005 from a conductive material having heat resistance, and it may be formed from a single layer, or it may also have a lamination structure made from a plurality of layers, such as two layers or three layers, when necessary. For example, the conductive layer 1005 may be formed by an element selected from the group consisting of tungsten (W), tantalum (Ta), titanium (Ti), and molybdenum (Mo), or from an alloy with the above elements as constituents, or from an alloy film of a combination of the above elements. Further, the conductive layer 1005 may be formed with a lamination structure with a nitride compound of the above elements, such as tungsten nitride (WN), tantalum nitride (TaN), titanium nitride (TIN), or molybdenum nitride (MoN), or a silicide compound such as tungsten silicide, tantalum silicide, titanium silicide, or molybdenum silicide. A first shape mask 1006 is formed next. The first shape mask 1006 is formed by a photolithography technique using a resist material.

[0094] Etching of the conductive layer 1005 is performed next, as shown by FIG. 1B. The etching process is formed the tapered shape and performed to obtain the tapered portion at the edge portion of the conductive layer 1005 by use of the first shape mask. The etching process is performed using a dry etching method, preferably by using an ICP etching apparatus. A gas mixture of  $\mathrm{CF_4}$  and  $\mathrm{Cl_2}$  is used as an etching gas, and a bias voltage is applied to the substrate. A conductive layer 1008 having a first tapered shape on at least the island-like semiconductor layer 1003 is formed. The shape of the tapered portion can be changed in accordance with the etching gas mixture ratio, with the etching pressure, and with the bias voltage applied to the substrate. The bias voltage applied to the substrate is most able to control the tapered shape.

[0095] Dry etching is performed by elements such as fluorine (F) and chlorine (CI), or by neutral particles or ionic particles of molecules containing fluorine or chlorine. Normally, etching proceeds in an isotropic manner if it is controlled by neutral particles, and a tapered shape is difficult to form. Etching proceeds in an anisotropic manner by applying a positive or a negative bias voltage to the substrate. Etching for forming a tapered shape is performed by applying a bias voltage to the substrate, and by etching the resist at the same time, with the difference in etching speed between the film and the resist (also referred to as selectivity ratio, and expressed as the etching speed of the process piece/etching speed of resist) having a value in a certain fixed range. By first making an appropriate resist shape, and then etching gradually from an edge portion of the resist, a tapered shape can be formed in the film underneath. The shape of the first shape mask 1006 also changes, forming a second shape mask 1007. Further, as etching proceeds, the surface of the gate insulating film 1004 under the conductive layer 1005 is exposed, and the gate insulating film is also etched to a certain extent from its surface, forming a second shape gate insulating film 1009.

[0096] The resist 1009 is then used as a mask, and a first doping process is performed. A single conductivity type impurity element is added to the island-like semiconductor layer 1003. An ion doping method or an ion injection method in which the impurity element is ionized, accelerated by an electric field, and then injected into the semiconductor layer is performed as the doping process. The single conductivity type impurity element passes through the gate insulating film

and is added to the semiconductor layer beneath. A portion of the single conductivity type impurity element can be added to the semiconductor layer passing through an edge portion and the vicinity of the conductive layer 1008 having the first tapered shape.

[0097] A first impurity region 1011 contains a concentration of the single conductivity type impurity element from  $1\times10^{20}$  to  $1\times10^{21}$  atoms/cm<sup>3</sup>. Further, the concentration of the impurity element added to the semiconductor layer in a second impurity region (A) 1012 is lower, compared to that of the first impurity region 1011 by the amount that the thickness of the second shape gate insulating film 1009 increases. A uniform concentration distribution is not always able to be obtained within the second impurity region (A) 1012, but the impurity element is added so as to be within a range of  $1\times10^{17}$  to  $1\times10^{20}$  atoms/cm<sup>3</sup>.

[0098] An enlarged view of a region 1017 surrounded by a dotted line in FIG. 1B is shown in FIG. 2A-1. Further, FIG. 2A-2 is a diagram which schematically expresses the concentration distribution of the impurity element in arbitrary units. The impurity region is formed under the gate insulating film and the tapered portion of the gate electrode. The concentration distribution of the impurity element is shown by a line 1030, and decreases with the distance from the first impurity region 1011. The ratio of the decrease differs depending on the acceleration voltage and the dosage amount during ion doping, and with an angle  $\theta 1$  of the tapered portion and the thickness of the first shape gate electrode 1008.

[0099] A second etching process is performed next, as shown in FIG. 1C. The second etching process is an anisotropic etching and etches the first shape gate electrode 1008 so as to make the width of the channel longitudinal direction shorter. The method of etching is the same as that of the first etching process, and an ICP etching apparatus is used. A gas mixture of CF<sub>4</sub> and Cl<sub>2</sub> is used as an etching gas, and a bias voltage is applied to the substrate, forming a conductive layer 1015 having a second tapered shape. In the second etching process also, a portion of the gate insulating film as a base film is etched from the surface thereby formed a gate insulating film 1016 having the second tapered shape. An enlarged view of a region 1019 enclosed by a dotted line is shown in FIG. 1C, and although a tapered portion is also formed in an edge portion of the second tapered shape conductive layer 1015, a taper angle 62 becomes larger than  $\theta 1$  because of the etching process in which the width of the channel longitudinal direction has been made shorter.

[0100] The resist 1014 is then used as a mask, a second doping process is performed, and a single conductivity type impurity element is added to the island-like semiconductor layer 1003. In this case, a portion of the impurity element can passes through the edge portion of the second tapered shape conductive layer 1015 and its vicinity, and can be added to the semiconductor layer below.

[0101] The second doping process is performed so that the single conductivity type impurity element is contained at a concentration of  $1\times10^{16}$  to  $5\times10^{18}$  atoms/cm³ in the semiconductor layer. As also shown in FIG. 2B-2, the single conductivity type impurity element is added by this process to the first impurity region 1011 and to the second impurity region (A) 1012 formed by the first doping process but the amount added is low, and therefore its influence can be ignored. A newly formed second impurity region (B) 1018 is made to contain the single conductivity type impurity element at a concentration of  $1\times10^{16}$  to  $5\times10^{18}$  atoms/cm³. The second

impurity region (B) 1018 reduces the concentration of the impurity element added to the semiconductor layer by the amount that the thickness of the second tapered shape conductive layer 1016 increases, and although a uniform concentration distribution cannot necessarily be obtained within the second impurity region (B) 1018, the impurity element is contained within the above concentration range.

[0102] The second impurity region (B) 1018 is formed under the second shape gate insulating film 1016 and nuder the tapered portion of the second tapered shape conductive layer 1015. Its concentration distribution of the impurity element is shown by a line 1031, and decreases with a distance from the first impurity region 1011. The second tapered shape conductive layer 1015 is used as a gate electrode. By making the edge portion of the gate electrode having a tapered shape, and by doping the impurity element through the tapered portion, an impurity region can thus be formed in the semiconductor layer existing under the tapered portion in which the concentration of the impurity element changes gradually. The present invention actively utilizes this impurity region. By forming this type of impurity region, a high electric field developing in the vicinity of the drain region is relieved, then the deterioration of the TFT can be prevented because of generation of hot carriers.

[0103] Thus the first impurity region which becomes a source region or a drain region, the second impurity region (A) which forms the LDD region not overlapping the gate electrode, the second impurity region (B) which forms the LDD region overlapping a portion of the gate electrode, and a channel forming region 1023 are formed in the island-like semiconductor layer 1003. Then, when necessary, an interlayer insulating film 1020 may be formed, and a wiring 1021 which contacts with the source region or the drain region may be formed, as shown in FIG. 1D.

# Embodiment 1

[0104] An Embodiment of the present invention is explained using FIGS. 3A to 5B. A method of manufacturing a pixel TFT and a storage capacitor of a pixel portion, and a driver circuit TFT formed in the periphery of the pixel portion, at the same time is explained in detail here in accordance with process steps.

[0105] In FIG. 3A, a glass substrate such as barium borosilicate glass or aluminum borosilicate glass, typically Corning Corp. #7059 or #1737 glass, or a quartz substrate is used as a substrate 101. When using a glass substrate, heat treatment may be performed in advance at a temperature between 10 and 20 EC below the distortion temperature of the glass. A base film 102 is then formed from an insulating film such as a silicon oxide film, a silicon nitride film, or a silicon nitride oxide film on the surface of the substrate 101 on which a TFT will be formed, in order to prevent impurity element diffusion. For example, a lamination of a silicon nitride oxide film 102a having a thickness of 10 to 200 nm (preferably between 50 and 100 nm) and manufactured by plasma CVD using SiH<sub>4</sub>, NH<sub>3</sub>, and N<sub>2</sub>O, and a hydrogenated silicon nitride oxide film 102b having a thickness of 50 to 200 nm (preferably between 100 and 150 nm) and manufactured similarly from SiH<sub>4</sub> and N<sub>2</sub>O is formed. A two layer structure is shown for the base film 102 here, but a single layer film of the above insulating films, or a lamination film having more than two layers may also be formed.

[0106] The silicon nitride oxide film is formed using a parallel plate type plasma CVD method. For the silicon

nitride oxide film 102a,  $SiH_4$ ,  $NH_3$ , and  $N_2O$  are introduced to a reaction chamber at 10 SCCM, 100 SCCM, and 20 SCCM, respectively, the substrate temperature is set to 325 EC, the reaction pressure is 40 Pa, the emission power density is set to  $0.41 \text{ W/cm}^2$ , and the emission frequency is 60 MHz. On the other hand, for the hydrogenated silicon nitride oxide film 102b,  $SiH_4$ ,  $N_2O$ , and  $H_2$  are introduced to the reaction chamber at 5 SCCM, 120 SCCM, and 125 SCCM, respectively, the substrate temperature is set to 400 EC, the reaction pressure is 20 Pa, the emission power density is set to  $0.41 \text{ W/cm}^2$ , and the emission frequency is 60 MHz. These films can be formed in succession by changing the substrate temperature and switching the reaction gasses.

[0107] The silicon nitride oxide film 102a thus manufactured has a density of  $9.28\times10^{22}/\text{cm}^3$ , has a slow etching speed of approximately 63 nm/min when etched by a mixed solution containing 7.13% ammonium bifluoride (NH<sub>4</sub>HF<sub>2</sub>) and 15.4% ammonium fluoride (NH<sub>4</sub>F) (Stella Chemifor Corp. product name LAL500) at 20 EC. If this type of film is used in the base film, then the base film is effective in preventing diffusion of alkaline metal elements from the glass substrate into the semiconductor layer formed on the base film.

[0108] Next, a semiconductor layer 103a having an amorphous structure is formed by a method such as plasma CVD or sputtering to a thickness of 20 to 80 nm (preferably between 30 and 60 nm). Amorphous semiconductor layers and microcrystalline semiconductor films exist in semiconductor films having an amorphous structure, and a chemical compound semiconductor film having an amorphous structure such as an amorphous silicon germanium film may also be applied. When forming an amorphous silicon film by plasma CVD, it is possible to form both the base film 102 and the amorphous semiconductor layer 103a in succession. For example, as stated above, after forming the silicon nitride oxide film 102a and the hydrogenated silicon nitride oxide film 102b successively by plasma CVD, the amorphous semiconductor layer 103a can be formed in succession without exposure to the atmosphere by switching the reaction gasses from SiH<sub>4</sub>, N<sub>2</sub>O, and H<sub>2</sub> to SiH<sub>4</sub> and H<sub>2</sub>. As a result, it becomes possible to ward off contamination of the surface of the hydrogenated silicon nitride oxide film 102b, and a dispersion in the characteristics of the manufactured TFTs and fluctuations in their threshold voltage can be lowered.

[0109] A crystallization process is then performed, and a crystalline semiconductor layer 103b is manufactured from the amorphous semiconductor layer 103a. Laser annealing, thermal annealing (solid state growth method), and rapid thermal annealing (RTA method) can be applied as the crystallization method. When using a glass substrate such as those stated above, or a plastic substrate with inferior heat resistance, it is particular preferable to apply laser annealing. An light source such as an infrared lamp, a halogen lamp, a metal halide lamp, or a xenon lamp is used by the RTA method. Alternatively, the crystalline semiconductor layer 103b can be formed by a crystallization method using a catalytic element, in accordance with a technique disclosed by Japanese Patent Application Laid-open No. Hei 7-130652. In this crystallization process, first it is preferable to release hydrogen contained in the amorphous semiconductor layer, and if the crystallization is performed after the amount of hydrogen contained is made equal to or less than 5 atom % by performing heat treatment at 400 to 500 EC for approximately 1 hour, then roughness of the film surface can be prevented.

[0110] Further,  $\mathrm{SiH_4}$  and  $\mathrm{argon}$  (Ar) are used in a reaction gas in a process of forming an amorphous silicon film by plasma CVD, and if the substrate temperature is set from 400 to 450 EC at the time of film deposition, then the concentration of hydrogen contained within the amorphous silicon film can also be made equal to or less than 5 atomic %. The heat treatment for releasing hydrogen becomes unnecessary in this case

[0111] When performing crystallization by laser annealing, a pulse emission type or a continuous emission type excimer laser, or an argon laser is used as the light source. Laser light is processed into a linear shape and then laser annealing is performed when using a pulse emission type excimer laser. The conditions of laser annealing may be suitably determined by the operator, but for example, the laser pulse emission frequency is set to 30 Hz, and the laser energy density is set from 100 to 500 mJ/cm² (typically between 300 and 400 mJ/cm²). The linear shape beam is then irradiated over the entire surface of the substrate, and this is performed with an overlap ratio of 80 to 98% for the linear shape beam. Thus the crystalline semiconductor layer 103b can be obtained, as shown in FIG. 3B.

[0112] A resist pattern is then formed using a photolithography technique employing a first photomask PM1 on the crystalline semiconductor layer 103b. The crystalline semiconductor layer is then partitioned into island-like shapes by dry etching, forming the island-like semiconductor layers 104 to 108, as shown in FIG. 3C. A gas mixture of CF<sub>4</sub> and O<sub>2</sub> is used in the dry etching of the crystalline silicon film.

[0113] An impurity element which imparts p-type conductivity may then be added at a concentration of  $1 \times 10^{16}$  to  $5\times10^{17}$  atoms/cm<sup>3</sup> to the entire surface of the island-like semiconductor layers, with an aim of controlling the threshold voltage (Vth) of the TFTs. Elements existing in periodic table group 13, such as boron (B), aluminum (Al), and gallium (Ga) are known as impurity elements which will impart p-type conductivity with respect to semiconductors. Ion injection and ion doping (or ion shower doping) can be used as the method of adding the impurity element, though ion doping is suitable for processing a large surface area substrate. Boron (B) is added by ion doping using diborane (B<sub>2</sub>H<sub>6</sub>) as a source gas. This type of impurity element injection is not always necessary and may be omitted without any hindrance. In particular it is a method appropriately used in order to keep the threshold voltage of an n-channel TFT within a predetermined range.

[0114] A gate insulating film 109 is formed with a thickness of 40 to 150 nm from an insulating film containing silicon by plasma CVD or sputtering. In Embodiment 1, a 120 nm thick silicon nitride oxide film is used to form the gate insulating film 109. Further, a silicon nitride oxide film formed by adding O<sub>2</sub> to SiH<sub>4</sub> and N<sub>2</sub>O has a reduced fixed charge density within the film therefore it is a preferable material for this type of use. Furthermore, a silicon nitride oxide film manufactured from SiH<sub>4</sub>, N<sub>2</sub>O and H<sub>2</sub> has a lowered defect density in the boundary with the gate insulating film, which is preferable. Of course, as the gate insulating film is not limited to this type of silicon nitride oxide film, other insulating films containing silicon may also be used, in a single layer or a multiple layer structure. For example, when using a silicon oxide film, it can be formed by plasma CVD with a mixture of TEOS (tetraethyl orthosilicate) and O<sub>2</sub>, at a reaction pressure of 40 Pa, with the substrate temperature set from 300 to 400 EC, and by discharging at a high frequency (13.56 MHz) electric power density of 05 to  $0.8~\rm W/cm^2$ . Good characteristics as a gate insulating film can be obtained by subsequently performing thermal annealing of the silicon oxide film thus manufactured at 400 to 500 EC.

[0115] A heat resistant conductive layer 111 for forming a gate electrode is then formed with a thickness of 200 to 400 nm (preferably between 250 and 350 nm) on the first shape gate insulating film 109, as shown in FIG. 3D. The heat resistant conductive layer may be formed by a single layer and may also be a lamination structure composed of a plurality of layers such as a two layers or three layers structure, when necessary. In this specification, the heat resistant conductive layer contains an element chosen from the group consisting of Ta, Ti, W and Mo or an alloy of the above elements, or an alloy film of a combination of said elements. These heat resistant conductive layers are formed by sputtering or CVD, and it is preferable to reduce the impurity element concentration contained in order to make the resistance low. In particular, it is preferable to make the concentration of oxygen equal to or less than 30 ppm. A 300 nm thick W film is formed in Embodiment 1. The W film may be formed by sputtering with W as a target, and can also be formed by thermal CVD using tungsten hexafluoride (WF<sub>6</sub>). Whichever is used, it is necessary to be able to make the film become low resistance in order to use as the gate electrode, and it is preferable that the resistivity of the W film be made equal to or less than 20  $\Omega$ cm. The resistivity can be lowered by enlarging the crystals of the W film, but for cases in which there are a many impurity elements such as oxygen within the W film, crystallization is inhibited, and the film becomes high resistance. Thus a W target having a purity of 99.9999% is used in sputtering, and by additionally forming the W film taking sufficient care so as not to introduce any impurities from within the gas phase at the time of film deposition, a resistivity of 9 to 20  $\Omega$ cm can be achieved.

[0116] When using a Ta film in the heat resistant conductive layer, it is possible to form the Ta film similarly by sputtering. Ar is used in the sputtering gas for the Ta film. Further, if an appropriate amount of Xe and Kr are added to the gas at the time of sputtering, then the internal stress of the film formed is relaxed, and film peeling can be prevented. The resistivity of an  $\alpha$  phase Ta film is on the order of 20  $\Omega$ cm, and it can be used in the gate electrode, but the resistivity of a  $\alpha$  phase Ta film is on the order of 180  $\Omega$ cm and it is unsuitable for the gate electrode. A TaN film possesses a crystal structure which is close to that of  $\alpha$  phase Ta film, and therefore an  $\alpha$  phase Ta film can easily be obtained provided that a TaN film is formed under the Ta film. Further, although not shown in the figures, it is effective to form a silicon film doped by phosphorous (P) and having a thickness on the order of 2 to 20 nm under the heat resistant conductive layer 111. By doing that increasing the adhesion and preventing oxidation of the conductive film formed on top, at the same time alkaline metal elements contained in the heat resistant conductive layer 111 in microscopic amounts can be stopped from diffusing into the first shape gate insulating film 109 by doing so. Whichever is used, it is preferable that the resistivity of the heat resistant conductive layer 111 be in a range from 10 to 50  $\Omega$ cm.

[0117] Next, masks 112 to 117 are resists formed by a photolithography technique using a second photomask PM2. A first etching process which is a taper etching is then performed. The etching is performed in Embodiment 1 using an ICP etching apparatus, using Cl<sub>2</sub> and CF<sub>4</sub> as etching gasses, inputting an RF (13.56 MHz) power of 3.2 W/cm<sup>2</sup> at 1 Pa of

pressure to form a plasma. A 224 mW/cm<sup>2</sup> RF (13.56 MHz) power is also introduced to the substrate side (sample stage), and therefore a negative self bias voltage is effectively applied. The etching speed of the W film is approximately 100 m/min under these conditions. The etching time in order to exactly etch the W film is estimated based on this etching speed, further an etching time for the first etching process is set at 20% more greater than the estimated etching time.

[0118] Conductive layers having a first tapered shape 118 to 123 are formed by the first etching process. The angle of the tapered portions is formed from 15 to 30 E similar to that shown by FIG. 2A. In order to perform etching without leaving any residual, over etching is performed in which the etching time is increased by a ratio on the order of 10 to 20%. The selectivity of a silicon nitride oxide film (the first shape gate insulating film 109) with respect to the W film is between 2 and 4 (typically 3), and therefore the exposed surface of the silicon nitride oxide film is etched on the order of 20 to 50 nm by the over etching process, and a second shape gate insulating film 134, in which a tapered shape is formed in near the edge portion of the conductive layer having the first tapered shape, is formed.

[0119] A first doping process is then performed, adding a single conductivity type impurity element into the island-like semiconductor layers. A process of adding an impurity element which imparts n-type conductivity is performed here. The masks 112 to 117 for forming the first shape conductive layers are left as it is, and with the first tapered shape conductive layers 118 to 123 are used as a mask, the impurity element which imparts n-type conductivity is added by ion doping in a self-aligning manner. The ion doping is performed using a dosage amount of  $1 \times 10^{13}$  to  $5 \times 10^{14}$  atoms/cm<sup>2</sup> and with the acceleration voltage set between 80 and 160 keV in order for the n-type conductivity imparting impurity element to be added so as to pass through the tapered portion in the edge portion of the gate electrode and through the gate insulating film, and so as to reach the semiconductor layers placed below. An element residing in periodic table group 15 is used as the impurity element which imparts n-type conductivity, typically phosphorous (P) or arsenic (As), and phosphorous (P) is used here. The impurity element which imparts n-type conductivity is added to first impurity regions 124 to 128 here by the ion doping process at a concentration in the range of  $1\times10^{20}$  to  $1\times10^{21}$  atoms/cm<sup>3</sup>. Although there is not necessarily a uniform concentration within second impurity regions (A) formed below the tapered portion, the n-type conductivity imparting impurity element is added within a range of  $1 \times 10^{17}$ to  $1 \times 10^{20}$  atoms/cm<sup>3</sup>.

[0120] The change in concentration of the n-type conductivity imparting impurity element contained in a portion of second impurity regions (A) 129 to 133 overlapping at least the first shape conductive layers 118 to 123 reflects the change in thickness of the tapered portion. In other words, the concentration of phosphorous (P) added to the second impurity regions (A) 129 to 133 gradually becomes less from the edge portion of the conductive layers toward the inside in the region overlapping with the first shape conductive layers. The concentration of phosphorous (P) reaching the semiconductor layers changes due to the difference in a film thickness of the tapered portion, and that the concentration change is as shown in FIG. 2A-2.

[0121] A second etching process which is an anisotropic process is performed next, as shown in FIG. 4B. The etching process is also similarly performed by an ICP etching apparatus.

ratus with a mixed gas of  $\mathrm{CF_4}$  and  $\mathrm{Cl_2}$  used in the etching gas, the etching is performed with an RF power of 3.2 W/cm² (13.56 MHz), a bias power of 45 mW/cm² (13.56 MHz), and at a pressure of 1.0 Pa. Conductive layers having a second shape 140 to 145 formed under this conditions are formed. A tapered portion is formed in each edge portions, and this becomes a tapered shape in which the thickness gradually increases from the edge portion toward the inside. Compared with the first etching process, the ratio of anisotropic etching becomes greater in the substrate side by the amount that the applied bias power is reduced, and the angle of the tapered portion becomes from 30 to 60°. Further, the surface of the second shape gate insulating film 134 is etched on the order of 40 nm, newly forming a third shape gate insulating film 170.

[0122] An impurity element which imparts n-type conductivity is then doped at conditions of a dosage amount lower than that of the first doping process, and at a high acceleration voltage. For example, the acceleration voltage is set between 70 and 120 keV, and doping is performed with a dosage amount of  $1\times10^{13}$  atoms/cm<sup>2</sup>, so as to make the impurity concentration in a region overlapping with the second shape seniconductive layers 140 to 145 be from  $1\times10^{16}$  and  $1\times10^{18}$  atoms/cm<sup>3</sup>. Second impurity regions (B) 146 to 150 are thus formed

[0123] Impurity regions 156 and 157, having a conductivity type which is the inverse of the single conductivity type impurity element, are then formed in the island-like semiconductor layers 104 and 106 which form p-channel TFTs. The second shape conductive layers 140 and 142 are used as a mask in this case as well, and an impurity element which imparts p-type conductivity is added. The impurity regions are formed in a self-aligning manner. The island-like semiconductor layers 105, 107, and 108, which form n-channel TFTs, are covered over their entire surfaces by resist masks 151 to 153, formed using a third photomask PM3. Impurity regions 156 and 157 formed here are formed by ion doping using diborane (B<sub>2</sub>H<sub>6</sub>). The concentration of the p-type conductivity imparting impurity element in the impurity regions 156 and 157 is set so as to become  $2\times100$  to  $2\times10^{21}$  atoms/ cm<sup>3</sup>.

[0124] However, in detail the impurity regions 156 and 157 can be seen as being divided into three regions containing n-type conductivity imparting impurity elements. Third impurity regions 156a and 157a contain the impurity element which imparts n-type conductivity at a concentration of  $1\times10^2$  to  $1\times10^{21}$  atoms/cm<sup>3</sup>, fourth impurity regions (A) **156**b and 157b contain to the impurity element which imparts n-type conductivity at a concentration of  $1 \times 10^{17}$  and  $1 \times 10^{20}$ atoms/cm<sup>3</sup>, and fourth impurity regions (B) **156**c and **157**c contain a concentration of the n-type conductivity imparting impurity element from  $1\times10^{16}$  and  $1\times10^{18}$  atoms/cm<sup>3</sup>. However, the concentration of the impurity element which imparts p-type conductivity is set so as to be equal to or greater than  $1\times10^{19}$  atoms/cm<sup>3</sup> in the impurity regions 156b, 156c, 157b, and 157c, and in the third impurity regions 156a and 157a, the concentration of the p-type conductivity imparting impurity element is made to be from 1.5 to 3 times as high, and therefore no problems will develop when the third impurity regions function as a source region and a drain region of a p-channel TFT. Further, a portion of the fourth impurity regions (B) 156c and 157c is formed so as to overlap with a portion of the second tapered shape conductive layer 140 or

[0125] Next, as shown in FIG. 5A, a first interlayer insulating film 158 is formed on the gate electrode and the gate insulating film. The first interlayer insulating film may be formed by a silicon oxide film, a silicon nitride oxide film, a silicon nitride film, or a lamination film of a combination of these films. Whichever is used, the first interlayer insulating film 158 is formed from an inorganic insulating material. The film thickness of the first interlayer insulating film 158 is set from 100 to 200 nm. When using a silicon oxide film here, it can be formed by plasma CVD with a mixture of TEOS and O<sub>2</sub>, at a reaction pressure of 40 Pa, with the substrate temperature set from 300 to 400 EC, and by discharging at a high frequency (13.56 MHz) electric power density of 0.5 to 0.8 W/cm<sup>2</sup>. Further, when using a silicon nitride oxide film, the silicon nitride oxide film may be manufactured by plasma CVD from SiH<sub>4</sub>, N<sub>2</sub>O, and NH<sub>3</sub>, and the silicon nitride oxide film may be manufactured from SiH<sub>4</sub> and N<sub>2</sub>O. The manufacturing conditions in this case are a reaction pressure of 20 to 200 Pa, a substrate temperature set from 300 to 400° C., and the film can be formed by applying a high frequency (60 MHz) electric power density of 0.1 to 1.0 W/cm<sup>2</sup>. Further, a hydrogenated silicon nitride oxide film manufactured from SiH<sub>4</sub>, N<sub>2</sub>O, and H<sub>2</sub> may also be applied. It is also possible to manufacture a silicon nitride film from SiH<sub>4</sub>, and NH<sub>3</sub> similarly by plasma CVD.

[0126] A process of activating the n-type and p-type conductivity imparting impurity element added at their respective concentrations is then performed. Thermal annealing using an annealing furnace is performed for this process. In addition, laser annealing and rapid thermal annealing (RTA) can also be applied. Thermal annealing is performed with an oxygen concentration equal to or less than 1 ppm, preferably equal to or less than 0.1 ppm, in a nitrogen atmosphere at 400 to 700° C., typically between 500 and 600° C. Heat treatment is performed for 4 hours at 550° C. in Embodiment 1. Further, it is preferable to apply laser annealing when a plastic substrate having a low heat resistance temperature is used as the substrate 101.

[0127] After the activation process the gas atmosphere is changed, and heat treatment is performed for 1 to 12 hours at 300 to 450° C. in an atmosphere containing between 3 and 100% hydrogen, performing hydrogenation of the island-like semiconductor layers. This process is one of terminating from 10<sup>16</sup> to 10<sup>18</sup>/cm³ of dangling bonds in the island-like semiconductor layers by hydrogen which is thermally excited. Plasma hydrogenation (using hydrogen excited by a plasma) may also be performed as another means of hydrogenation. Whichever is used, it is preferable to reduce the defect density within the island-like semiconductor layers 104 to 108 to 10<sup>16</sup>/cm³ or less, and hydrogen may be imparted on the order of 0.01 to 0.1 atomic %.

[0128] By forming a second interlayer insulating film from an organic insulating material, the surface can be made very level. Further, an organic resin material generally has a low dielectric constant therefore the parasitic capacitance can be reduced. However, it absorbs moisture and is not suitable as a protecting film therefore it is used in combination with the first interlayer insulating film 158 formed by a film such as a silicon oxide film, a silicon nitride oxide film, or a silicon nitride film.

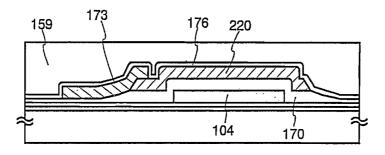

[0129] Next, a resist mask is formed with a predetermined pattern using a fourth photomask PM4, and contact holes are formed in each of the island-like semiconductor layers in order to reach the impurity regions formed as source regions

or drain regions. The contact holes are formed by dry etching. In this case, a second interlayer insulating film **159** made from an organic resin material is etched using a gas mixture of  $CF_4$ ,  $O_2$ , and He. Afterward, the first interlayer insulating film **158** is etched in succession using an etching gas of  $CF_4$  and  $O_2$ . In addition, the contact holes can be formed by etching the third shape gate insulating film **170**, where the etching gas is switched to  $CHF_3$  in order to increase the selectivity with the island-like semiconductor layers.

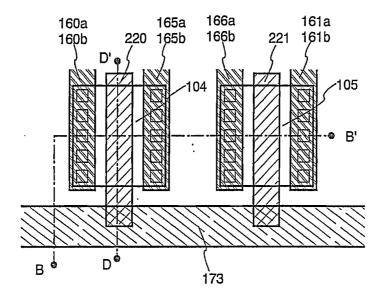

[0130] A conductive metallic film is then formed by sputtering or vacuum evaporation, and a resist mask pattern is formed by a fifth photomask PM5. Source lines 160 to 164 and drain lines 165 to 168 are formed by etching. A pixel electrode 169 is formed with the drain lines. A pixel electrode 171 denotes a pixel electrode belonging to a neighboring pixel Although not shown in the figures, in Embodiment 1 Ti films are formed with a thickness of 50 to 150 nm, contacts with the impurity regions forming the source or drain regions of the island-like semiconductor layers is formed, aluminum (Al) films having a thickness of 300 to 400 nm is formed on the Ti film (shown by reference numerals 160a to 169a in FIG. 5B and in addition, transparent conductive films with a thickness of 80 to 120 nm are formed on the aluminum film (shown by reference numerals **160***b* to **169***b* in FIG. **5**C) for the wirings. An indium oxide zinc oxide alloy (In<sub>2</sub>O<sub>3</sub>—ZnO) or zinc oxide (ZnO) is the material applied suitably to the transparent conductive film, and in addition, a material such as zinc oxide in which gallium (Ga) has been added (ZnO:Ga) in order to increase the transitivity of optical light and to increase the conductivity can also be used preferably.

[0131] The substrate, having the driver circuit TFTs and the pixel TFTs of the pixel portion on the same substrate, can thus be completed by using 5 photomasks. A first p-channel TFT 200, a first n-channel TFT 201, a second p-channel TFT 202, and a second n-channel TFT 203 are formed in the driver circuit, and a pixel TFT 204 and a storage capacitor 205 are formed in the pixel portion. This type of substrate is referred to as an active matrix substrate throughout this specification for convenience.

[0132] In the first p-channel TFT 200 of the driver circuit, a conductive layer having the second tapered shape functions as a gate electrode 220. The structure of the island-like semiconductor layer 104 has a channel forming region 206, a third impurity region 207a which functions as a source region or a drain region, a fourth impurity region (A) 207b which forms an LDD region not overlapping the gate electrode 220, and a fourth impurity region (B) 207c which forms an LDD region overlapping a portion of the gate electrode 220.

[0133] In the first n-channel TFT 201, a conductive layer having the second tapered shape functions as a gate electrode 221. The structure of the island-like semiconductor layer 105 has a channel forming region 208, a first impurity region 209a which functions as a source region or a drain region, a second impurity region (A) 209b which forms an LDD region not overlapping the gate electrode 221, and a second impurity region (B) 209c which forms an LDD region overlapping a portion of the gate electrode 221. The length of the portion in which the second impurity region (B) 209c overlaps the gate electrode 221 is set from 0.1 to 0.3 • with respect to a channel length of 2 to 7 This length Lov is controlled by the thickness of the gate electrode 221 and by the angle of the tapered portion. By forming this type of LDD region in an n-channel TFT, the high electric field which develops near the drain

region is relieved, and the development of hot carriers is blocked, then deterioration of the TFT can be prevented.

[0134] In the second p-channel TFT 202 of the driver circuit, a conductive layer having the second tapered shape similarly functions as a gate electrode 222. The structure of the island-like semiconductor layer 106 has a channel forming region 210, a third impurity region 211a which functions as a source region or a drain region, a fourth impurity region (A) 211b which forms an LDD region not overlapping the gate electrode 222, and a fourth impurity region (B) 211c which forms an LDD region overlapping a portion of the gate electrode 222

[0135] In the second n-channel TFT 203 of the driver circuit, a conductive layer having the second tapered shape functions as a gate electrode 223. The structure of the island-like semiconductor layer 107 has a channel forming region 212, a first impurity region 213a which functions as a source region or a drain region, a second impurity region (A) 213b which forms an LDD region not overlapping the gate electrode 223, and a second impurity region (B) 213c which forms an LDD region overlapping a portion of the gate electrode 223. The length of the portion in which the second impurity region (B) 213c overlaps the gate electrode 223 is set similar to that of the second n-channel TFT 201, from 0.1 to 0.3.

[0136] The driver circuit is formed by logic circuits such as a shift register circuit and a buffer circuit, and by circuits such as a sampling circuit formed by an analog switch. In FIG. 5B, TFTs for forming these circuits are shown by a single gate structure in which one gate electrode is formed between a source and drain pair, but a multi-gate structure in which a plurality of gate electrodes are formed between source and drain pairs may also be used without hindrance.

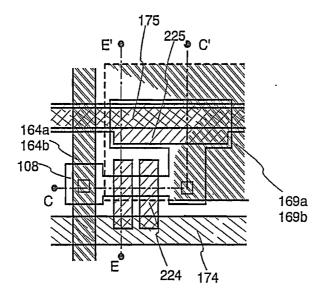

[0137] In the pixel TFT 204 of the driver circuit, a conductive layer having the second tapered shape functions as a gate electrode 224. The structure of the island-like semiconductor layer 108 has channel forming regions 214a and 214b, first impurity region 215a and 217 which function as source regions or drain regions, a second impurity region (A) 215b which forms an LDD region not overlapping the gate electrode 224, and a second impurity region (B) 215c which forms an LDD region overlapping a portion of the gate electrode 224. The length of the portion in which the second impurity region (B) 213c overlaps the gate electrode 224 is set from 0.1 to 0.3. Further, a storage capacitor is formed from: a semiconductor layer which extends from the first impurity region 217 and has a second impurity region (A) 219b, a second impurity region (B) 219c, and a region 218 to which is not added impurity elements determining the conductivity type; an insulating layer formed by the same layer as the gate insulating film having the third shape; and a capacitor wiring 225 formed from the second tapered shape conductive layer. [0138] FIG. 11 is a top view showing approximately one pixel of the pixel portion. A cross section along the line A-A shown in the figure corresponds to the cross sectional diagram of the pixel portion shown in FIG. 5B. In the pixel TFT 204, a gate electrode 224 intersects, through a gate insulating film not shown in the figure, with the island-like semiconductor layer 108 formed below and stretches over a plurality of island-like semiconductor layers furthermore to serve as the gate wiring. Although not shown in the figure, a source region, a drain region, and an LDD region are formed in the island-like semiconductor layers, as explained by FIG. 5B. Further, reference numeral 230 denotes a contact portion of the source wiring 164 and the source region 215a, reference numeral 231 denotes a contact portion of the pixel electrode 169 and a drain region 217. The storage capacitor 205 is formed by a region in which the semiconductor layer extending from the drain region 217 of the pixel TFT 204 and the capacitor wiring 225 overlap, through the gate insulating film. An impurity element for controlling valence electrons is not added in the semiconductor layer 218 in this structure.

[0139] A structure such as that above optimizes the structure of the pixel TFT and TFTs composing each circuits of the driver circuit in response to the specifications required, and it is possible to increase the operating performance and the reliability of the semiconductor device. In addition, by forming the gate electrode using a conductive material having heat resistance, the LDD regions, and source regions and drain regions are easily activated. Moreover, when forming the LDD region overlapping the gate electrode through the gate insulating film, in particular it can be expected that the relieving effect for the electric field formed near the drain region will increase by forming the LDD region to possess a concentration gradient of an impurity element added with the aim of controlling the conductivity type.

[0140] For a case of an active matrix type liquid crystal display device, the first p-channel TFT 200 and the first n-channel TFT 201 are used to form circuits such as a shift register circuit, a buffer circuit, and a level shifter circuit which place importance on high speed operation. In FIG. 5B, these circuits are denoted as a logic circuit portion. The second impurity region (B) 209c of the first n-channel TFT 201 becomes a structure which places importance on counteracting hot carriers. In addition, in order to increase voltage resistance and stabilize operation, the TFTs of the logic circuit portion may also be formed by a first p-channel TFT 280 and a first n-channel TFT 281, as shown by FIG. 9A. These TFTs have a double gate structure in which two gate electrodes are formed between one source and drain pair, and this type of TFT can be similarly manufactured by using the processes of Embodiment 1. The structure of the first p-channel TFT 280 has channel forming regions 236a and 236b, third impurity regions 238a, 239a, and 240a which function as source or drain regions, fourth impurity regions (A) 238b, 239b, and 240b which become LDD regions, and fourth impurity regions (B) 238c, 239c, and 240c which become LDD regions overlapping a portion of a gate electrode 237 in the island-like semiconductor layer. The structure of the first n-channel TFT 281 has channel forming regions 241a and 241b, first impurity regions 243a, 244a, and 245a which function as source or drain regions, second impurity regions (A) **243***b*, **244***b*, and **245***b* which become LDD regions, and second impurity regions (B) 243c, 244c, and 245c which become LDD regions overlapping a portion of a gate electrode 242 in the island-like semiconductor layer. Taking the length of the LDD region which overlaps the gate electrode as Lov, its length in the longitudinal direction of the channel is set from 0.1 to 0.3 • with respect to a channel length of 3 to 7

[0141] Further, in a sampling circuit structured by analog switches, similarly structured second p-channel TFTs 202 and second n-channel TFTs 203 can be applied. The sampling circuit places importance on measures against hot carriers and low Off current operation therefore the TFT of this circuit may be formed by a second p-channel TFT 282 and a second n-channel TFT 283 as shown by FIG. 9B. The second p-channel TFT 282 has a triple gate structure in which three gate

electrodes are formed between one source and drain pair, and this type of TFT can be similarly manufactured by using the processes of Embodiment 1. The structure of the second p-channel TFT 282 has channel forming regions 246a, 246b, and **246***c*, third impurity regions **249***a*, **250***a*, **251***a*, and **252***a* which function as source or drain regions, fourth impurity regions (A) 249b, 250b, 251b, and 252b which become LDD regions, and fourth impurity regions (B) 249c, 250c, 251c, and 252c which become LDD regions overlapping a portion of a gate electrode 247. The structure of the second n-channel TFT **283** has channel forming regions **253**a and **253**b, first impurity regions 255a, 256a, and 257a which function as source or drain regions, second impurity regions (A) 255b, 256b, and 2576 which become LDD regions, and second impurity regions (B) 255c, 256c, and 257c which become LDD regions overlapping a portion of a gate electrode 254. Taking the length of the LDD region which overlaps the gate electrode as Lov, its length in the longitudinal direction of the channel is set from 0.1 to 0.3 • with respect to a channel length of 3 to 7 •.

[0142] Thus, whether to use a single gate structure for the structure of the TFT gate electrode, or to use a multi-gate structure in which a plurality of gate electrodes are formed between one source and drain pair, may be suitably determined by the operator, in accordance with the circuit characteristics. A reflecting type liquid crystal display device can then be manufactured by using the active matrix substrate completed in Embodiment 1.

# Embodiment 2

[0143] Examples of using heat-resistant conductive materials such as W and Ta as materials for the gate electrode were shown in Embodiment 1. The reason for using these materials resides in that it is necessary to activate the impurity element that was doped into the semiconductor layer for the purpose of controlling the conductive type after the formation of the gate electrode by thermal annealing at between 400° C. and 700° C. By implementing this step, it is necessary that the gate electrode has heat-resistivity. However, this type of heatresistant conductive material has a sheet resistivity of about 10 W, and hence is not always suitable for a display device having a screen size of a 4-inch class or more. This is because if a gate wiring to be connected to the gate electrode is formed of the same material, then the length of the lead wiring on the substrate inevitably becomes large. Thus, the problem of a wiring delay caused by the influence of wiring resistance cannot be ignored.

[0144] For example, 480 gate wirings and 640 source wirings are formed when the pixel density is VGA, and 768 gate wirings and 1024 source wirings are formed in the case of XGA. The screen size of the display region becomes 340 mm for a 13-inch class in diagonal length, and becomes 460 mm for an 18-inch class. In this embodiment, as a means of realizing this kind of liquid crystal display device, a method of forming the gate wiring from low-resistant conductive material such as Al and copper (Cu) will be explained using FIG. 6.

[0145] First, similar to Embodiment 1, the steps shown in FIGS. 3(A) to 4(C) will be performed. Then a step of activating the impurity element doped into the respective island semiconductor layers for the purpose of controlling the conductive type is performed. This step is performed by thermal annealing using an annealing furnace. In addition, laser annealing or rapid thermal annealing (RTA) can also be